-

[디지털시스템] Tail Light 제어기 설계Dream/전공과목 (전전) 2020. 9. 13. 02:56

1. Purpose

무어 상태 기계를 사용하여 자동차 신호등 제어기를 설계하는데 이때 신호등의 동작을 파악하여 최소개의 state로 Finite State Machine(FSM)을 설계해보도록 한다. 이를 통해 FSM과 state diagram, state transition table을 복습하고 설계에 이용해봄으로써 VHDL 코딩에 대한 보다 깊은 이해를 해보도록 한다.

2. Tail Light 제어기 설계

무어 상태 기계를 사용하여 자동차 신호등 제어기를 설계한다. 이때 신호등의 동작을 파악하여 최소개의 state로 FSM을 완성한다.

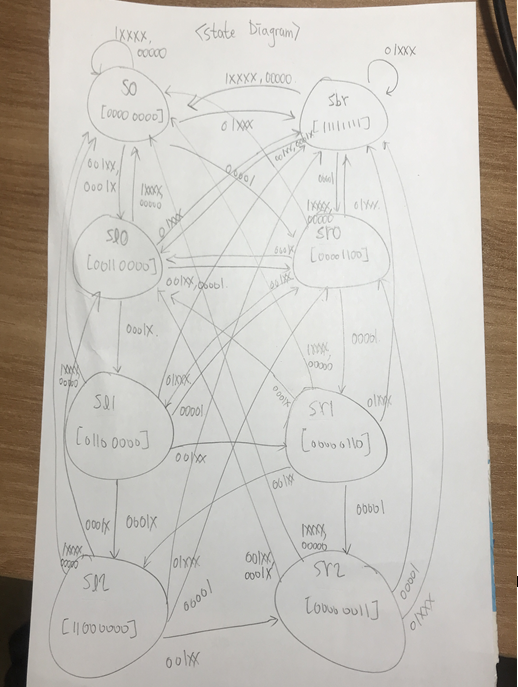

2-1) State Diagram

낡고 어두웠던 방에서 난 미래를 꿈꿨다. 2-2) State Transition Table

Current State

Input

(5bit vector)

Next State

Output

(8 bit LED)

S0

1xxxx

S0

0000 0000

00000

S0

01xxx

Sbr

001xx

Sl0

0001x

Sl0

00001

Sr0

Sbr

1xxxx

S0

1111 1111

00000

S0

01xxx

Sbr

001xx

Sl0

0001x

Sl0

00001

Sr0

Sl0

1xxxx

S0

0011 0000

00000

S0

01xxx

Sbr

001xx

Sr0

0001x

Sl1

00001

Sr0

Sl1

1xxxx

S0

0110 0000

00000

S0

01xxx

Sbr

001xx

Sr1

0001x

Sl2

00001

Sr0

Sl2

1xxxx

S0

1100 0000

00000

S0

01xxx

Sbr

001xx

Sr2

0001x

Sl0

00001

Sr0

Sr0

1xxxx

S0

0000 1100

00000

S0

01xxx

Sbr

001xx

Sl1

0001x

Sl0

00001

Sr1

Sr1

1xxxx

S0

0000 0110

00000

S0

01xxx

Sbr

001xx

Sl2

0001x

Sl0

00001

Sr2

Sr2

1xxxx

S0

0000 0011

00000

S0

01xxx

Sbr

001xx

Sl0

0001x

Sl0

00001

Sr0

3) Source code

주어진 과제는 주어진 신호등의 동작을 파악하여 최소개의 state로 무어 상태 기계를 사용하여 자동차 신호등 제어기를 설계하는 과제였다. 우선 IEEE library 및 std_logic_1164, Arith, UNSIGNED 패키지를 사용하고 entity를 선언한다. entity선을 통해 port들을 지정해 준 다음 8개의 state들로 이루어진 type states를 선언해준다. 그 후 state와 next_state 값을 states로 선언할 수 있게 해준 다음 문제에서 제시된 조건에 맞춰 무어 상태 기계를 이용하여 각 state에서의 next_state를 지정해준다. 그 이후 각 state에 따른 light의 상태를 지정해줌으로써 설계를 완성한다.

4) Test Bench

Test bench에서 iee library와 std_logic_11644 및 arith와 unsigned 패키지를 사용한다. 이후 앞서 설계했던 Tail_Light를 component로 불러온다음 각 port에 들어갈 signal들을 선언한다. 그리고 port map을 통해 각 signal들과 port들을 연결하고 clk을 설정해준다음 결과를 위해 주어진 조건 값들을 signal 값에 넣어준 다음 시뮬레이션을 실행한다.

5) Wave form

6) 고찰

이번 과제는 무어 상태 머신을 사용하여 자동차 신호등 제어기를 설계하는 실험이었다. 처음에 과제를 보았을 때는 사실 막막했었다. 뭔가 되게 어려워보이고 실제로 과제를 처음 봤을 때 사실 동작 원리가 잘 이해가 안되서 수업을 같이 듣는 친구에게 물어보면서 공부하면서 차근차근 스텝을 밟아가며 해보니 설계를 잘 마무리 할 수 있었다. 우선 제어기의 동작 상태 즉 제어기가 동작했을 시에 신호등의 상태를 무어 상태 머신을 통해 표현한 뒤 이를 코드로 정리해보았다. 상태는 reset, break, left 0,1,2, right 0,1,2 총 8가지의 상태로 설정하였다. Emergency 상태는 left와 right 상태를 한 번씩 번갈아가면서 작동시키는 것으로 간주하여 따로 상태는 만들지 않고 기존의 left 0~2와 right 0~2를 사용하여 설계하였다. 왜냐하면 이번 과제는 최소개의 state로 FSM을 설계해야하기 때문이다. 그러고 나서 설정한 상태를 바탕으로 state diagram을 그려준다. 사실 state diagram을 그렸을 때 그림이 엄청 복잡했어서 그리면서도 맞게 그리고 있는지 두 번이나 확인 했어야했다. 그 후 이를 state transition table로 작성하였다. state diagram과는 다르게 state transition table은 각 state에서 입력에 따른 next state를 나타낸 표이기 때문에 state diagram보다 작성이 훨씬 간편했다. 그 후 문제에서 주어진 대로 테스트벤치 코드를 작성한 후 결과를 확인한 결과 원하는 결과를 얻을 수 있었다.

이번 과제를 통해 주어진 상황을 해석하여 state를 설정하고 들어오는 모든 입력의 수를 따져 그 입력에 따른 next state를 설정하여 state diagram을 그리고 이를 다시 state trasition table로 작성한 후 논리적으로 재작성된 내부 구동원리에 맞춰 case문과 if문 등 다양한 VHDL 문법을 이용하여 이를 설계하고 최종적으로 이를 출력인 8비트 LED Light와 각 상태에 맞게 설정해줌으로써 원하는 결과를 얻을 수 있는 설계능력을 키울 수 있었다. 사실 이번 설계과제를 통해 많이 반성하게 되었다. 처음에는 지레짐작으로 어려워보여 더 공부하거나 도전할 생각은 하지 않고 ‘친구들에게 물어봐야지’하면서 안일하게 생각했었는데 사실 친구들에게 물어 같이 해보니 생각을 조금만 해보면 혼자서도 거뜬히 할 수 있는 과제였다. 다음에 또 과제나 프로젝트가 있다면 그때는 모르는 것이나 궁금한 것이 있어도 남에게 바로 물어보는 것이 아닌 조금 더 깊게 생각해보고 답을 직접 찾아보는 연습을 할 것이다.

'Dream > 전공과목 (전전)' 카테고리의 다른 글

[종합설계프로젝트] 공감각적 인지를 통한 시각장애인 감상 보조도구 (0) 2020.12.22 [디지털시스템] Procedure를 이용한 설계 - n-bit vector 내의 1의 개수를 출력하는 Numones procedure (0) 2020.09.13 [디지털시스템] Function을 이용한 설계 - n-bit vector의 2의 보수 형태를 출력하는 코드 (0) 2020.09.13 [디지털시스템] Design synchronous sequence detector which detects “0101” or “0110” sequence (0) 2020.09.13 [디지털시스템] Design 16-to-1 Multiplexer with 4-to-1 Multiplexer (0) 2020.09.13